HDLBits刷题日记(一)

打算利用碎片化时间重温一遍Verilog语法,好记性不如烂笔头,在此记录一下HDLBits刷题的过程,记录一些知识点,方便日后再次复习。

1、Getting Started

Problem 0 : Step one

Build a circuit with no inputs and one output. That output should always drive 1 (or logic high).

构建一个电路,没有输入端口,只有一个输出端口,输出端口时钟驱动逻辑 1 ,即逻辑高电平。

module top_module (

output one

);

assign one = 1'b1;

endmodule1 在数字逻辑中代表 logic high,而 0 代表 logic low。

Problem 1 : Zero

Build a circuit with no inputs and one output that outputs a constant 0.

构建一个电路,没有输入端口,只有一个输出端口,但这次输出端口时钟驱动逻辑 0 ,即逻辑低电平。

module top_module (

output zero

);

// Module body starts after semicolon

assign zero = 1'b0;

endmodule2、Verilog Language - Basics

Problem 2 : Wire

Create a module with one input and one output that behaves like a wire.

创建一个具有一个输入和一个输出的模块,其行为类似于导线(wire)。

不同于物理导线,Verilog中的导线(和其他信号)是有方向性的。这意味着信息只能从源(source)单向流向接收端(sink)(源通常也被称为驱动器,用于向导线驱动一个值)。在Verilog的"连续赋值"语句中(assign left_side = right_side;),右侧信号的值被驱动到左侧的导线上。这种赋值被称为"连续的",是因为即使右侧的值发生变化,赋值也会持续进行。连续赋值不是一次性的事件。

模块的端口也具有方向性(通常是输入或输出)。输入端口由模块外部的元件驱动,而输出端口则驱动模块外部的元件。从模块内部来看,输入端口是一个驱动器或源,而输出端口是一个接收端。

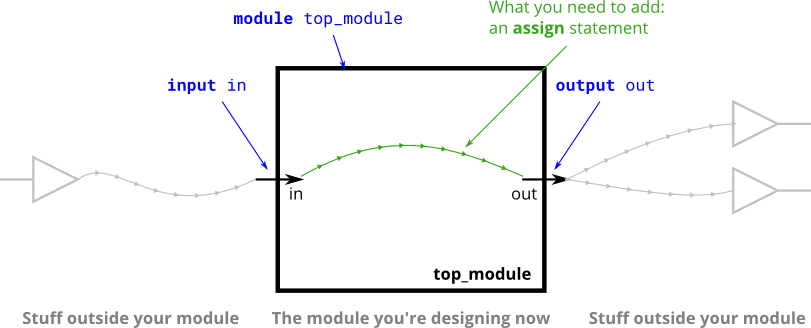

下图说明了电路的每个部分如何对应Verilog代码的每个位。模块和端口声明创建了电路的黑色部分。我们的任务是通过添加一个assign语句来创建一条导线(绿色部分),将输入(in)连接到输出(out)。模块外部的部分不是我们需要关心的,但应该知道,我们设计的电路将通过官方的测试工具连接到top_module的端口来进行测试。

module top_module (

input in,

output out

);

// Note that wires are directional, so "assign in = out" is not equivalent.

// 注意 wire 是有方向的 因此 assign in = out 是不等价的

assign out = in;

endmodulewire 一般只有一个 source,即从某一点输出,但可以有多个 sinks,即输入到多个点

assign 语句映射到具体的硬件上,就是产生了信号的驱动,由右值驱动左值。

Problem 3 : Wire4

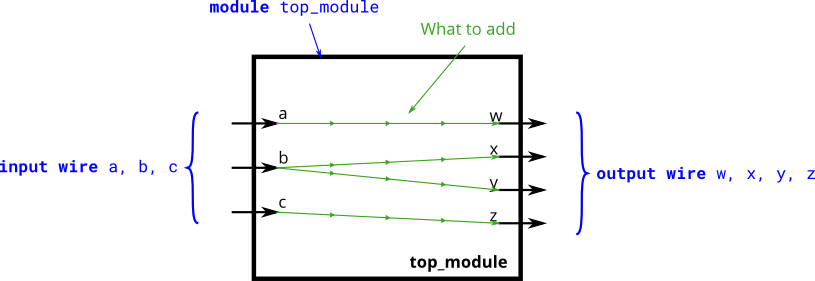

Create a module with 3 inputs and 4 outputs that behaves like wires that makes these connections:

创建一个具有3个输入和4个输出的模块,要实现如下连接:

a -> w

b -> x

b -> y

c -> z

module top_module(

input a,

input b,

input c,

output w,

output x,

output y,

output z

);

// 这里的顺序可以任意调换

assign w = a;

assign x = b;

assign y = b; // 注意这里 b 连接到两个输出

assign z = c;

endmodule多个 assign 语句的顺序并不重要,因为它们描述的是连接关系,而不是执行顺序。

输入输出端口声明会自动声明 wire 类型(除非特别指定其他类型),模块端口声明

input a等同于input wire a。assign 语句不是创建新的导线,而是在已存在的导线之间建立连接

注意 b 连接到了两个输出(x 和 y),这是允许的,因为一个输入信号可以驱动多个输出;虽然看起来有4条 assign 语句,但我们实际上是在7个已经存在的导线之间建立连接。