以太网之UART+MDIO

组里新买了一款开发板,打算借此重温基本外设的开发。本系列将结合相关芯片手册及个人理解,对 FPGA 开发以太网进行整理和记录。

1. 前言

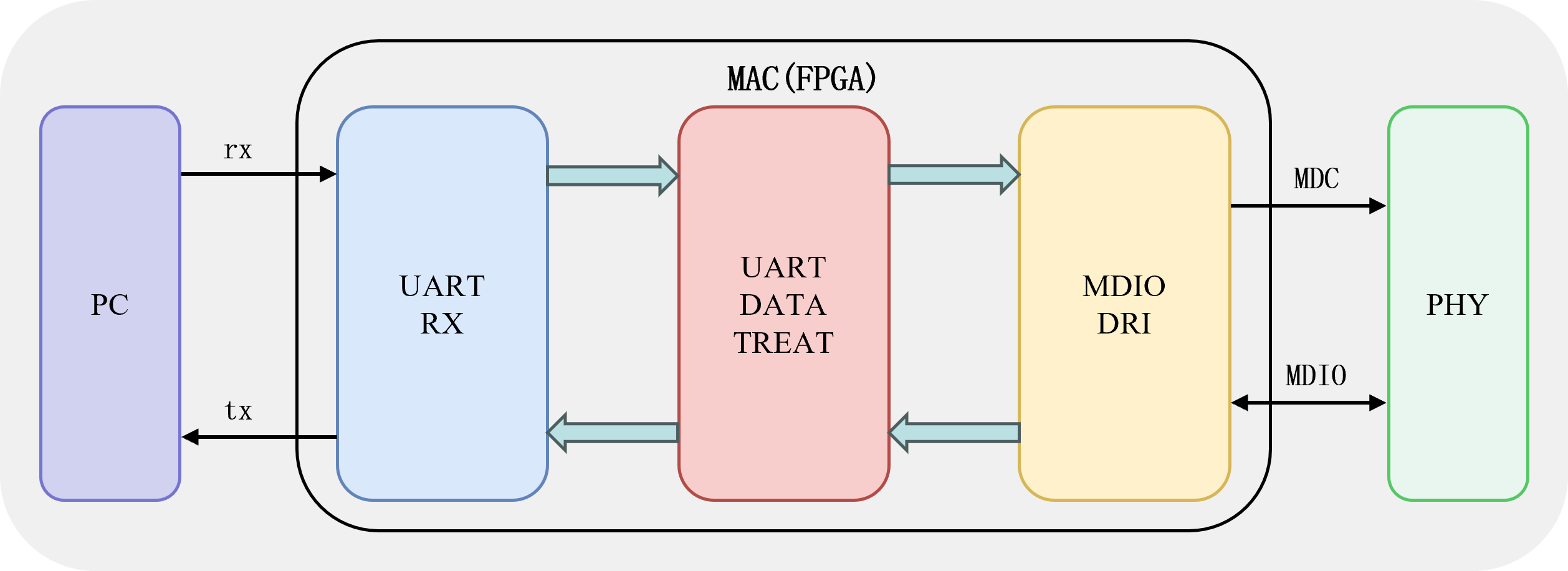

在前面的文章中,我们介绍了以太网中的 MDIO 的一些基本知识点,今天我们打算利用 UART 来控制 MDIO 的读写,PC 端通过 UART 向 FPGA 发送读写 PHY 芯片寄存器的指令,FPGA 通过 MDIO 总线从 PHY 芯片读取指定寄存器地址的数据后,通过 UART 将读取的数据发送到 PC 端的串口助手进行显示。

2 UART 收发

UART 的收发实现不属于本次文章的重点,具体实现可以参考UART 回环测试。

本次实验的指令格式定义如下:

串口读寄存器指令帧格式

| 字段名称 | 位宽 | 值/描述 | 字节序 |

|---|---|---|---|

| 帧起始符 | 8位 | 0x36 | 第1字节 |

| 设备地址 | 5位 | PHY 芯片地址 | 第2字节 |

| 无效位 | 2位 | 0x00 | 第2字节 |

| 读写指示 | 1位 | 0x01(最低位) | 第2字节 |

串口写寄存器指令帧格式

| 字段名称 | 位宽 | 值/描述 | 字节序 |

|---|---|---|---|

| 帧起始符 | 8位 | 0x36 | 第1字节 |

| 设备地址 | 5位 | PHY 芯片地址 | 第2字节 |

| 无效位 | 2位 | 0x00 | 第2字节 |

| 读写指示 | 1位 | 0x01(最低位) | 第2字节 |

| 写入数据 | 16位 | 高8位先写 | 3-4字节 |

3 整体设计介绍

这个处理流程相对简单,其思路和串口数据处理模块借鉴了 CSDN 上的电路_fpga 博主的文章 [1]。流程如下:PC 端通过串口模块发送数据,数据会先传输到串口数据处理模块进行解码,之后该模块会将解码后的信息传递给 MDIO 驱动模块。MDIO 驱动模块会驱动 PHY 芯片,实现对其内部寄存器的访问。

4 上板实测

4.1 网络连接

4.1 写操作

4.1 读操作

5、代码下载

博客中涉及到的代码均在我的GitHub仓库中,欢迎大家下载学习。

6、参考资料

以太网之UART+MDIO

https://yao-jiangyu.github.io/以太网之UATR+MDIO/